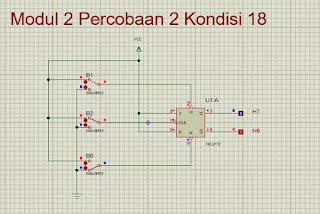

*Modul 2 Percobaan 2 Kondisi 18*

Buatlah rangkaian T flip flop seperti pada gambar pada percobaan 2 dengan ketentuan input B0=0, B1=1, B2=1

2. Gambar Rangkaian Simulasi

[Kembali]

3. Video Simulasi [Kembali]

4. Prinsip Kerja

[Kembali]

Pada rangkaian JK flip-flop, Dapat terlihat untuk kaki High SPDT terhubung ke Vcc dan kaki Low SPDT terhubung ke Ground. Input JK flip-flop terdiri dari J,K, dan CLK. dimana apabila J dan K berlogika 1&1 maka akan terjadi toggle. Toggle merupakan output pada JK flipflop (Q) selalu berubah ubah. pada CLK akan active low apabila terhubung ke ground untuk merubah output dari 1 ke 0 dan sebaliknya. Pada percobaan ini dapat terlihat kaki set high (logika 1) dari arus yang mengalir dari Vcc ke kaki B1 yang berlogika 1 dan diteruskan ke kaki S. dan reset low (logika 0) dari B2 yang berlogika 0 yang diteruskan ke kaki R, serta clock active high sehingga output yang keluar yang terbaca pada H7 dan H6 berlogika 0&1.

5. Link Download

[Kembali]

- Download HTML [klik disini]

- Download Rangkaian Simulasi [klik disini]

- Download Video Simulasi [klik disini]

- Download Datasheet 74LS112A [klik disini]

No comments:

Post a Comment