*Percobaan 1 Kondisi No. 8*

Buatlah sebuah rangkaian lengkap yang memuat 3 gerbang NAND dengan 2, 3 input dan 4 input, kemudian gerbang NOR dengan 2 dan 4 input,kemudian 1 gerbang XOR dan 1 gerbang XNOR. Dan output akhir rangkaian keseluruhannya ditunjukkan dengan LED atau LOGIC PROBE. Dimana input awal berupa 3 saklar SPDT.

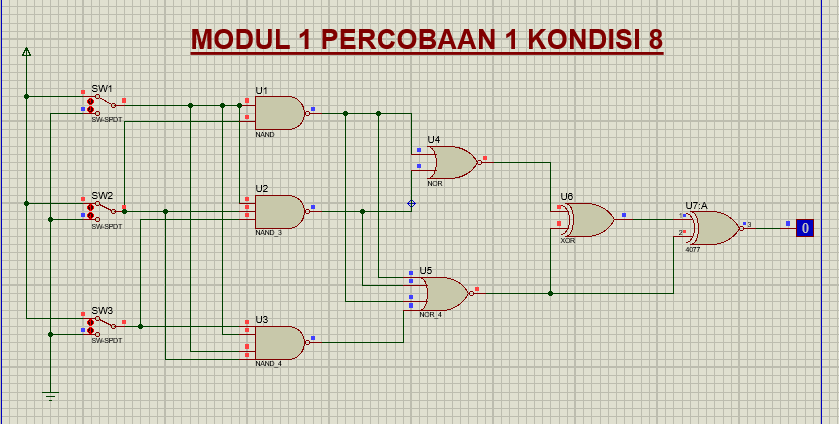

2. Gambar Rangkaian Simulasi

[Kembali]

Gambar 2. Rangkaian disimulasikan dengan

output akhir logika 1 (Variasi input SPDT : 1,1,0)

Gambar 3. Rangkaian disimulasikan dengan

output akhir logika 0 (Variasi input SPDT : 1,1,1)

3. Video Simulasi

[Kembali]

4. Prinsip Kerja

[Kembali]

- Kondisi 1 (output akhir logika 1)

Input awal SPDT terhubung ke VCC akan berlogika 1 sedangkan input yang terhubung ke Ground akan berlogika 0. Ketika saklar SPDT kita variasikan berlogika (1,1,0), maka outputnya akan berlogika 1 untuk SW1, logika 1 untuk output SW2, dan logika 0 untuk output SW3. Selanjutnya dapat kita lihat saklar SPDT terhubung ke gerbang NAND 2 input, 3 input dan 4 input. Gerbang NAND memiliki prinsip kerja yaitu jika menghasilkan keluaran logika 0 apabila semua masukan (input) berlogika 1 dan akan menghasilkan keluaran logika 1 apabila terdapat input yang berlogika 0. Atau simplenya gerbang NAND menggunakan prinsip perkalian kemudian di NOT kan.

Hal ini dapat kita lihat pada gerbang NAND U1(2 input), kaki 1-nya terhubung ke SW1 dan kaki 2-nya terhubung ke SW2. Pada kaki 1 gerbang NAND U1(2 input) mendapat input berlogika 1 dari output SW1 dan kaki 2 gerbang NAND U1(2 input) mendapat input berlogika 1 dari output SW 2. Untuk mendapatkan outputnya kita dapat terlebih dahulu menggunakan prinsip perkalian pada input gerbang NAND U1 (2 input). Dimana apa bila kita kalikan 1x1 = 1 dan kita NOT kan sehingga output yang keluar dari gerbang NAND U1(2 input) berlogika 0.

Selanjutnya dapat kita lihat pada gerbang NAND U2(3 input), kaki 1-nya terhubung ke SW1, kaki 2 terhubung ke SW2, dan kaki 3 terhubung ke SW3. Pada kaki 1 gerbang NAND U2(3 input) mendapat input berlogika 1 dari output SW1, kaki 2 gerbang NAND U2(3 input) mendapat input berlogika 1 dari output SW2, dan kaki 3 gerbang NAND U2(3 input) mendapat input berlogika 0 dari output SW3. Selanjutnya, kita dapat memperoleh output gerbang NAND U2(3 input) seperti yang telah dijelaskan sebelumnya dengan mengalikan inputnya yakni 1x1x0 = 0 dan hasilnya kita NOT kan. Sehingga output yang keluar dari gerbang NAND U2(3 input) berlogika 1.

Selanjutnya kita lihat gerbang NAND U3(4 input), kaki 1-nya terhubung ke output SW3, kaki 2 terhubung ke output SW1, kaki 3 terhubung ke output SW1 dan kaki 4 terhubung ke SW2. Pada kaki 1 gerbang NAND U3(4 input) mendapat input berlogika 0 dari output SW3, kaki 2 gerbang NAND U3(4 input) mendapat input berlogika 1 dari output SW1, kaki 3 gerbang NAND U3(4 input) mendapat input berlogika 1 dari output SW1, dan kaki 4 gerbang NAND U3(4 input) mendapat input berlogika 1 dari output SW1.

Kemudian, kita dapat memperoleh output gerbang NAND U3(4 input) seperti yang telah dijelaskan sebelumnya dengan mengalikan inputnya yakni 0x1x1x1 = 0 dan di NOT kan sehingga output yang keluar dari gerbang NAND U3(4 input) berlogika 1. Kemudian output dari gerbang NAND U1(2 input), NAND U2(3 input), dan NAND U3(4 input) akan masuk ke kaki input gerbang NOR U4(2 input) dan NOR U5(4 input). Pada gerbang NOR prinsip kerjanya yaitu ketika inputnya berlogika 0 semuanya maka outputnya berlogika 1 dan apabila terdapat inputnya berlogika 1, maka outputnya akan berlogika 0 .

Hal ini dapat terlihat pada gerbang NOR U4(2 input), kaki 1-nya terhubung ke output gerbang NAND U1(2 input) dan kaki 2 terhubung ke output gerbang NAND U2(3 input). Pada kaki 1 gerbang NOR U4(2 input) mendapat input berlogika 0 dari ouput gerbang NAND U1(2 input) dan kaki 2 gerbang NOR U4(2 input) mendapat input berlogika 1 output gerbang NAND U2(3 input). Maka kita dapat memperoleh outputnya dengan memakai prinsip yang telah dijelaskan tadi, dimana terdapat input berlogika 1 pada masukan gerbangnya sehingga output yang keluar dari gerbang NOR U4(2 input) berlogika 0.

Kemudian pada gerbang NOR U5(4 input), kaki 1-nya terhubung ke ouput gerbang NAND U1(2 input), kaki 2 terhubung ke output gerbang NAND U2(3 input), kaki 3 terhubung ke ouput gerbang NAND U1(2 input), dan kaki 4 terhubung ke output gerbang NAND U3(4 input). Pada kaki 1 gerbang NOR U5(4 input) mendapat input berlogika 0 dari ouput gerbang NAND U1(2 input), kaki 2 gerbang NOR U5(4 input) mendapat input berlogika 1 output gerbang NAND U2(3 input) kaki 3 gerbang NOR U5(4 input) mendapat input berlogika 0 dari ouput gerbang NAND U1(2 input), dan kaki 4 gerbang NOR U5(4 input) mendapat input berlogika 1 dari ouput gerbang NAND U3(4 input). Kemudian, kita dapat memperoleh outputnya dengan memakai prinsip yang telah dijelaskan tadi, dimana terdapat input berlogika 1 pada masukan gerbangnya sehingga output yang keluar dari gerbang NOR U5(4 input) berlogika 0.

Selanjutnya, output dari gerbang NOR U4(2 input) dan output gerbang NOR U5(4 input) akan masuk ke kaki input XOR U6(2 input). Pada gebang XOR, prinsip kerjanya ialah ketika jumlah input berlogika 1 berjumlah ganjil (1,3,5,dst) maka outputnya berlogika 1, sebaliknya jika jumlah input berlogika 1 berjumlah genap (0,2,4,dst) maka outputnya berlogika 0. Hal ini dapt terlihat pada gerbang XOR U6(2 input), dimana kaki 1 terhubung ke output gerbang NOR U4(2 input) dan kaki 2 terhubung ke output gerbang NOR U5(4 input). Pada kaki 1 gerbang XOR U6(2 input) mendapat input berlogika 0 dari output gerbang NOR U4(2 input) dan kaki 2 gerbang XOR U6(2 input) mendapat input berlogika 0 dari output gerbang NOR U5(4 input). Kemudian, kita dapat memperoleh output dari gerbang XOR U6(2 input) dimana jumlah input berlogika 1 yang masuk pada gerbang XOR U6(2 input) berjumlah genap sehingga output yang dikeluarkan pada gerbang XOR U6(2 input) berlogika 0.

Terakhir, output pada gerbang XOR U6(2 input) dan gerbang NOR U5(4 input) akan masuk ke kaki input gerbang XNOR U7:A. Pada gerbang XNOR, prinsip kerjanya jika jika jumlah input berlogika 1 berjumlah genap (0,2,4,dst) maka outputnya berlogika 1, sebaliknya jika jumlah input berlogika 1 berjumlah ganjil (1,3,5,dst) maka outputnya berlogika 0.Hal ini dapt terlihat pada gerbang XNOR U7:A(2 input), dimana kaki 1 mendapat masukan dari output gerbang XOR U6(2 input) yang berlogika 0 sehingga input pada gerbang XNOR U7:A berlogika 0 dan kaki 2 mendapat masukan dari output gerbang NOR U5(4 input) yang berlogika 0 sehingga input pada gerbang XNOR U7:A berlogika 0. Selanjutnya, kita dapat memperoleh output pada gerbang XNOR U7:A dengan memakai prinsip tadi, dimana jumlah input yang berlogika 1 pada gerbang XNOR U7:A berjumlah genap maka output yang dikeluarkan pada gerbang XNOR U7:A berlogika 1 yang di tandai logic probe menampilkan output akhir dari rangkaian percobaan 1 kondisi 8 yang berlogika 1

- Kondisi 2 (output akhir logika 0)

Input awal SPDT terhubung ke VCC akan berlogika 1 sedangkan input yang terhubung ke Ground akan berlogika 0. Ketika saklar SPDT kita variasikan berlogika (1,1,1), maka outputnya akan berlogika 1 untuk SW1, logika 1 untuk output SW2, dan logika 1 untuk output SW3. Selanjutnya dapat kita lihat saklar SPDT terhubung ke gerbang NAND 2 input, 3 input dan 4 input. Gerbang NAND memiliki prinsip kerja yaitu jika menghasilkan keluaran logika 0 apabila semua masukan (input) berlogika 1 dan akan menghasilkan keluaran logika 1 apabila terdapat input yang berlogika 0. Atau simplenya gerbang NAND menggunakan prinsip perkalian kemudian di NOT kan.

Hal ini dapat kita lihat pada gerbang NAND U1(2 input), kaki 1-nya terhubung ke SW1 dan kaki 2-nya terhubung ke SW2. Pada kaki 1 gerbang NAND U1(2 input) mendapat input berlogika 1 dari output SW1 dan kaki 2 gerbang NAND U1(2 input) mendapat input berlogika 1 dari output SW 2. Untuk mendapatkan outputnya kita dapat terlebih dahulu menggunakan prinsip perkalian pada input gerbang NAND U1 (2 input). Dimana apa bila kita kalikan 1x1 = 1 dan kita NOT kan sehingga output yang keluar dari gerbang NAND U1(2 input) berlogika 0.

Selanjutnya dapat kita lihat pada gerbang NAND U2(3 input), kaki 1-nya terhubung ke SW1, kaki 2 terhubung ke SW2, dan kaki 3 terhubung ke SW3. Pada kaki 1 gerbang NAND U2(3 input) mendapat input berlogika 1 dari output SW1, kaki 2 gerbang NAND U2(3 input) mendapat input berlogika 1 dari output SW2, dan kaki 3 gerbang NAND U2(3 input) mendapat input berlogika 1 dari output SW3. Selanjutnya, kita dapat memperoleh output gerbang NAND U2(3 input) seperti yang telah dijelaskan sebelumnya dengan mengalikan inputnya yakni 1x1x1 = 1 dan hasilnya kita NOT kan. Sehingga output yang keluar dari gerbang NAND U2(3 input) berlogika 0.

Selanjutnya kita lihat gerbang NAND U3(4 input), kaki 1-nya terhubung ke output SW3, kaki 2 terhubung ke output SW1, kaki 3 terhubung ke output SW1 dan kaki 4 terhubung ke SW2. Pada kaki 1 gerbang NAND U3(4 input) mendapat input berlogika 1 dari output SW3, kaki 2 gerbang NAND U3(4 input) mendapat input berlogika 1 dari output SW1, kaki 3 gerbang NAND U3(4 input) mendapat input berlogika 1 dari output SW1, dan kaki 4 gerbang NAND U3(4 input) mendapat input berlogika 1 dari output SW1.

Kemudian, kita dapat memperoleh output gerbang NAND U3(4 input) seperti yang telah dijelaskan sebelumnya dengan mengalikan inputnya yakni 1x1x1x1 = 1 dan di NOT kan sehingga output yang keluar dari gerbang NAND U3(4 input) berlogika 0. Kemudian output dari gerbang NAND U1(2 input), NAND U2(3 input), dan NAND U3(4 input) akan masuk ke kaki input gerbang NOR U4(2 input) dan NOR U5(4 input). Pada gerbang NOR prinsip kerjanya yaitu ketika inputnya berlogika 0 semuanya maka outputnya berlogika 1 dan apabila terdapat inputnya berlogika 1, maka outputnya akan berlogika 0 .

Hal ini dapat terlihat pada gerbang NOR U4(2 input), kaki 1-nya terhubung ke output gerbang NAND U1(2 input) dan kaki 2 terhubung ke output gerbang NAND U2(3 input). Pada kaki 1 gerbang NOR U4(2 input) mendapat input berlogika 0 dari ouput gerbang NAND U1(2 input) dan kaki 2 gerbang NOR U4(2 input) mendapat input berlogika 0 output gerbang NAND U2(3 input). Maka kita dapat memperoleh outputnya dengan memakai prinsip yang telah dijelaskan tadi, dimana tidak terdapat input berlogika 1 pada masukan gerbangnya sehingga output yang keluar dari gerbang NOR U4(2 input) berlogika 1.

Kemudian pada gerbang NOR U5(4 input), kaki 1-nya terhubung ke ouput gerbang NAND U1(2 input), kaki 2 terhubung ke output gerbang NAND U2(3 input), kaki 3 terhubung ke ouput gerbang NAND U1(2 input), dan kaki 4 terhubung ke output gerbang NAND U3(4 input). Pada kaki 1 gerbang NOR U5(4 input) mendapat input berlogika 0 dari ouput gerbang NAND U1(2 input), kaki 2 gerbang NOR U5(4 input) mendapat input berlogika 0 output gerbang NAND U2(3 input) kaki 3 gerbang NOR U5(4 input) mendapat input berlogika 0 dari ouput gerbang NAND U1(2 input), dan kaki 4 gerbang NOR U5(4 input) mendapat input berlogika 0 dari ouput gerbang NAND U3(4 input). Kemudian, kita dapat memperoleh outputnya dengan memakai prinsip yang telah dijelaskan tadi, dimana tidak terdapat input berlogika 1 pada masukan gerbangnya sehingga output yang keluar dari gerbang NOR U5(4 input) berlogika 1.

Selanjutnya, output dari gerbang NOR U4(2 input) dan output gerbang NOR U5(4 input) akan masuk ke kaki input XOR U6(2 input). Pada gebang XOR, prinsip kerjanya ialah ketika jumlah input berlogika 1 berjumlah ganjil (1,3,5,dst) maka outputnya berlogika 1, sebaliknya jika jumlah input berlogika 1 berjumlah genap (0,2,4,dst) maka outputnya berlogika 0. Hal ini dapt terlihat pada gerbang XOR U6(2 input), dimana kaki 1 terhubung ke output gerbang NOR U4(2 input) dan kaki 2 terhubung ke output gerbang NOR U5(4 input). Pada kaki 1 gerbang XOR U6(2 input) mendapat input berlogika 1 dari output gerbang NOR U4(2 input) dan kaki 2 gerbang XOR U6(2 input) mendapat input berlogika 1 dari output gerbang NOR U5(4 input). Kemudian, kita dapat memperoleh output dari gerbang XOR U6(2 input) dimana jumlah input berlogika 1 yang masuk pada gerbang XOR U6(2 input) berjumlah genap sehingga output yang dikeluarkan pada gerbang XOR U6(2 input) berlogika 0.

Terakhir, output pada gerbang XOR U6(2 input) dan gerbang NOR U5(4 input) akan masuk ke kaki input gerbang XNOR U7:A. Pada gerbang XNOR, prinsip kerjanya jika jika jumlah input berlogika 1 berjumlah genap (0,2,4,dst) maka outputnya berlogika 1, sebaliknya jika jumlah input berlogika 1 berjumlah ganjil (1,3,5,dst) maka outputnya berlogika 0.Hal ini dapt terlihat pada gerbang XNOR U7:A(2 input), dimana kaki 1 mendapat masukan dari output gerbang XOR U6(2 input) yang berlogika 0 sehingga input pada gerbang XNOR U7:A berlogika 0 dan kaki 2 mendapat masukan dari output gerbang NOR U5(4 input) yang berlogika 1 sehingga input pada gerbang XNOR U7:A berlogika 1. Selanjutnya, kita dapat memperoleh output pada gerbang XNOR U7:A dengan memakai prinsip tadi, dimana jumlah input yang berlogika 1 pada gerbang XNOR U7:A berjumlah ganjil maka output yang dikeluarkan pada gerbang XNOR U7:A berlogika 0 yang di tandai logic probe menampilkan output akhir dari rangkaian percobaan 1 kondisi 8 yang berlogika 0

5. Link Download

[Kembali]

No comments:

Post a Comment